STM32——NVIC中断优先级管理分析

前言

个人认为本篇文章是我作总结的最好的一篇,用自己的话总结出来清晰易懂,给小白看也能一眼明了,这就是写博客的意义吧。本篇文章具体介绍了 NVIC中断优先级管理,是如何进行管理,如何根据优先级响应中断的。本篇文章仅作为个人学习笔记总结,不做权威标准。

一、中断如何响应?NVIC如何分配优先级?

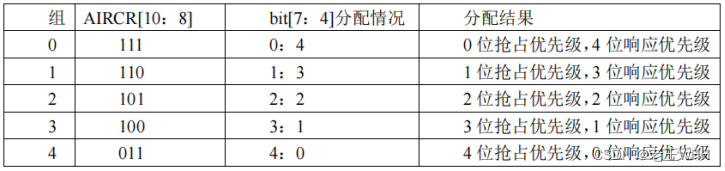

那么是如何响应的呢?中断占用8bit,但是只用高四位。优先级分组为4位,有以下的分组方式:0-4,1-3,2-2,3-1,4-0,这几组中分别是响应优先级和抢占优先级的分组,例如1-3,就是响应优先级为1,抢占优先级为3。

1.抢占优先级的级别>响应优先级级别

2.数值越小优先级越高

3.抢占优先级与响应优先级都一样,那么看哪个中断先发生。

4.高优先级的抢占优先级的中断可以打断低抢占优先级的中断,但是高优先级的响应优先级的中断不能够打断低响应优先级的中断。

例子:假定设置中断优先级组为 2,然后设置中断 3(RTC 中断)的抢占优先级为 2,响应优先级为 1。中断 6(外部中断 0)的抢占优先级为 3,响应优先级为 0。中断 7(外部中断 1)的抢占优先级为 2,响应优先级为 0。那么这 3 个中断的优先级顺序为:中断 7>中断 3>中断 6。

上面例子中的中断 3 和中断 7 都可以打断中断 6 的中断。而中断 7 和中断 3 却不可以相互打断!

二、NVIC中断优先级管理详解

详细NVIC中断优先级管理,以下是正点原子的详细介绍:(上面懂了下面不用看)

CM3 内核支持 256 个中断,其中包含了 16 个内核中断和 240 个外部中断,并且具有 256 级的可编程中断设置。但 STM32 并没有使用 CM3 内核的全部东西,而是只用了它的一部分。 STM32 有 84 个中断,包括 16 个内核中断和 68 个可屏蔽中断,具有 16 级可编程的中断优先级。而我们常用的就是这 68 个可屏蔽中断,但是 STM32 的 68 个可屏蔽中断,在 STM32F103 系列上面,又只有 60 个(在 107 系列才有 68 个)。

在 MDK 内,与 NVIC 相关的寄存器,MDK 为其定义了如下的结构体:

typedef struct

{

__IOM uint32_t ISER[8U];

uint32_t RESERVED0[24U];

__IOM uint32_t ICER[8U];

uint32_t RSERVED1[24U];

__IOM uint32_t ISPR[8U];

uint32_t RESERVED2[24U];

__IOM uint32_t ICPR[8U];

uint32_t RESERVED3[24U];

__IOM uint32_t IABR[8U];

uint32_t RESERVED4[56U];

__IOM uint8_t IP[240U];

uint32_t RESERVED5[644U];

__OM uint32_t STIR;

} NVIC_Type;

STM32 的中断在这些寄存器的控制下有序的执行的。只有了解这些中断寄存器,才能方便 的使用 STM32 的中断。下面重点介绍这几个寄存器:

-

ISER[8]:ISER 全称是:Interrupt Set-Enable Registers,这是一个中断使能寄存器组。上面说了 CM3 内核支持 256 个中断,这里用 8 个32 位寄存器来控制,每个位控制一个中断。但是STM32F103 的可屏蔽中断只有 60 个,所以对我们来说,有用的就是两个(ISER[0]和 ISER[1]),总共可以表示 64 个中断。而 STM32F103 只用了其中的前 60 位。ISER[0]的 bit0~bit31 分别对应中断 0~31。ISER[1]的 bit0~27 对 应中断 32~59;这样总共 60 个中断就分别对应上了。你要使能某个中断,必须设置相应的 ISER 位为 1,使该中断被使能(这里仅仅是使能,还要配合中断分组、屏蔽、IO 口映射等设置才算是一个完整的中断设置)。具体每一位对应哪个中断,请参考 stm32f10x.h 里面的第 140 行处(针对编译器 MDK5 来说)。

-

ICER[8]:全称是:Interrupt Clear-Enable Registers,是一个中断除能寄存器组。该寄存器组与ISER 的作用恰好相反,是用来清除某个中断的使能的。其对应位的功能,也和 ICER 一样。这里要专门设置一个 ICER 来清除中断位,而不是向 ISER 写 0 来清除,是因为 NVIC 的这些寄存器都是写 1 有效的,写 0 是无效的。具体为什么这么设计,请看《CM3 权威指南》第 125 页,NVIC 概览一章。

-

ISPR[8]:全称是:Interrupt Set-Pending Registers,是一个中断挂起控制寄存器组。每个位对应的中断和 ISER 是一样的。通过置 1,可以将正在进行的中断挂起,而执行同级或更高级别的中断。写 0 是无效的。

-

ICPR[8]:全称是:Interrupt Clear-Pending Registers,是一个中断解挂控制寄存器组。其作用与 ISPR 相反,对应位也和 ISER 是一样的。通过设置 1,可以将挂起的中断接挂。写 0 无效。

-

IABR[8]:全称是:Interrupt Active Bit Registers,是一个中断激活标志位寄存器组。对应位所代表的中断和 ISER 一样,如果为 1,则表示该位所对应的中断正在被执行。这是一个只读寄存器,通过它可以知道当前在执行的中断是哪一个。在中断执行完了由硬件自动清零。

-

**IP[240]:全称是:Interrupt Priority Registers,是一个中断优先级控制的寄存器组。**这个寄存器组相当重要!STM32 的中断分组与这个寄存器组密切相关。IP 寄存器组由 240 个 8bit 的寄存器组成,每个可屏蔽中断占用 8bit,这样总共可以表示 240 个可屏蔽中断。而 STM32 只用到了其中的前 60 个。IP[59]~IP[0]分别对应中断 59~0。而每个可屏蔽中断占用的 8bit 并没有全部使用,而是只用了高 4 位。这 4 位,又分为抢占优先级和子优先级。抢占优先级在前,子优先级在后。而这两个优先级各占几个位又要根据 SCB->AIRCR 中的中断分组设置来决定。这里简单介绍一下 STM32 的中断分组:STM32 将中断分为 5 个组,组 0~4。该分组的设置是由 SCB->AIRCR 寄存器的 bit10~8 来定义的。

通过这个表,我们就可以清楚的看到组 0~4 对应的配置关系,例如组设置为 3,那么此时所有的 60 个中断,每个中断的中断优先寄存器的高四位中的最高 3 位是抢占优先级,低 1 位是响应优先级。每个中断,你可以设置抢占优先级为 0~7,响应优先级为 1 或 0。抢占优先级的级别高于响应优先级。而数值越小所代表的优先级就越高。

这里需要注意两点:第一,如果两个中断的抢占优先级和响应优先级都是一样的话,则看哪个中断先发生就先执行;第二,高优先级的抢占优先级是可以打断正在进行的低抢占优先级中断的。而抢占优先级相同的中断,高优先级的响应优先级不可以打断低响应优先级的中断。

中断优先级在程序中的配置:

以下是中断优先级设置的步骤:

①系统运行开始的时候设置中断分组。确定组号,也就是确定抢占优先级和响应优先级的 分配位数。设置函数为HAL_NVIC_PriorityGroupConfig。对于 HAL 库,在文件stm32f1xx_hal.c 内部定义函数 HAL_Init 中有调用 HAL_NVIC_PriorityGroupConfig 函数进行相关设置,所以我 们只需要修改 HAL_Init 内部对中断优先级分组设置即可。

② 设置单个中断的中断优先级别和使能相应中断通道,使用到的函数函数主要为函数HAL_NVIC_SetPriority 和函数HAL_NVIC_EnableIRQ。

三、问题汇总

1. ok,此时有人问了,如果中断的响应优先级和抢占优先级都一样呢?谁先发生?

根据ARM Cotex-M处理器的规范,中断请求的处理顺序将由唯一的硬件优先级标识符决定,即中断向量表中的位置。

2. 什么是中断向量表?

中断向量表中是一个存储中断服务程序地址的表格,每个中断都有唯一的中断号,每一个中断号对应中断向量表中的条目,中断号越低,此中断在表中的位置越靠前,就越先发生。

3. 我应该如何查看中断向量表?

芯片的数据手册或者参考手册,查找中断向量表的章节,查找中断向量表的起始位置,在KEIL5中搜索中断向量表的地址来查看。

4. 那么除了中断的响应优先级、抢占优先级、中断号,还有那些影响中断响应的因素呢?

中断处理函数的执行时间:如果执行时间很长,其他中断的请求有可能就被挂起,只有当前的中断处理函数执行完成,其他中断继续执行

中断屏蔽:前面简单介绍了几种中断,我们知道中断屏蔽某位置1,该中断就不能发生,即使优先级高也无法执行。

5. 那么问题又来了:某中断正在发生,是如何影响中断执行顺序的呢?

举例中断1和中断2,他们的响应和抢占相同,中断1触发但是执行时间很长,可能是数据处理运算,此时!2被触发,但是他俩响应和抢占相同,2就要等1处理完,此时2就被挂起,1结束后,NVIC就会查看在1执行的过程中是否有中断挂起,如果有就执行,这里就是2了。

6. 问题又又来了,1在执行2如何触发的:

通常情况下触发的原因是指:有中断源产生中断请求信号,那么中断被触发,此时不用考虑1是否在执行。

7. 问题又又又来了:中断触发的原因只有中断产生了中断请求这一种情况吗?

上个问题我们说到通常情况下是这样,那不通常呢?具体要取决于处理器的架构和中断控制器的功能。有以下触发原因:

1.软件触发中断:有些处理器允许软件生成中断请求信号,触发中断。

2.异常或错误中断:处理器发生异常、错误、故障的情况下,可能触发响应的中断。

3.调试中断:程序在debug调试的时候暂停,跳转,会响应中断。

8. 那么调试中断响应的是哪些中断?

1.调试监听中断

2.断点

3.数据观察暂停

如果小伙伴对NVIC中断优先级管理还有其他疑问欢迎留言讨论,如有错误还请指出!