(数字ic)CDC设计实例 - ICG :integrate Clock Gating Cell

CDC设计实例 - ICG :integrate Clock Gating Cell

1、Latch原理

锁存器(latch):所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态才被保存到输出,直到下一个锁存信号到来时才改变。

2、ICG消除毛刺原理

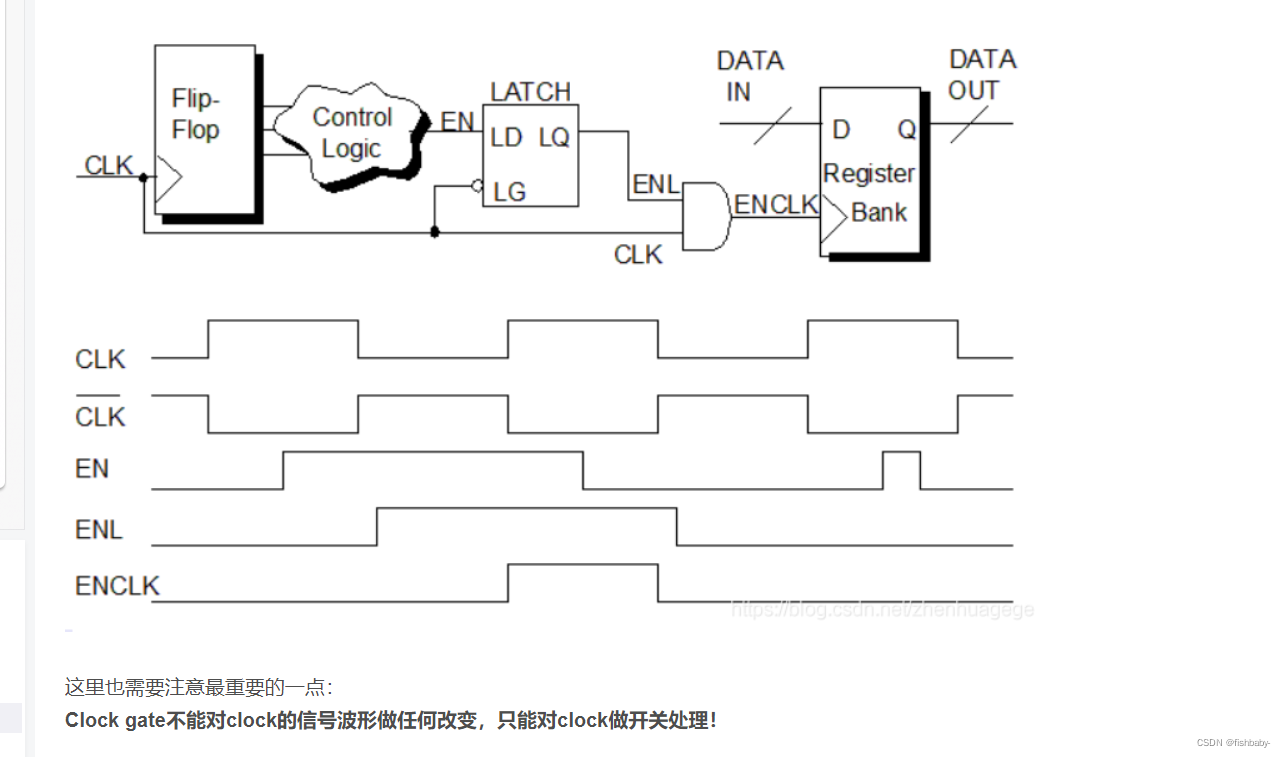

Clock gating cell 可以由与门或者或门构成,但是使用这两者会产生Glitch,因此目前都采用ICG(Integrated clock gating cell),其结构如下

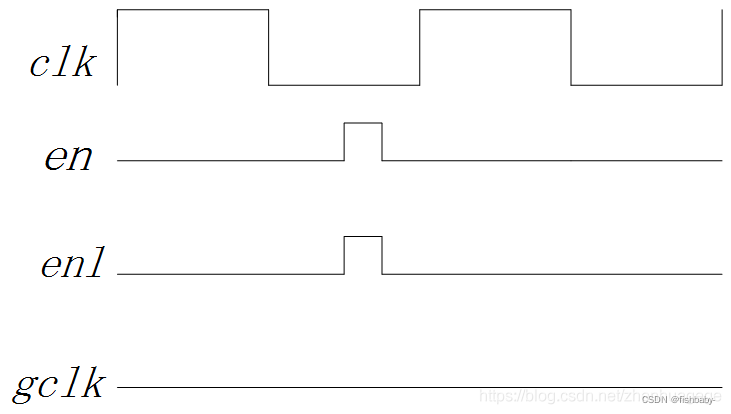

ICG由一个latch(低电平有效)和一个与门(gating cell,也可以是或门)组成。ICG 可以过滤掉en信号中的毛刺信号,其原理如下:

对于毛刺信号Glitch,大概可以分为两种情况:

1)en信号中的毛刺出现在clk低电平期间,如下图所示

由上图可以发现,en信号在clk低电平期间产生了毛刺,并且该latch是低电平有效,所以会采集到该毛刺信号,如信号enl中所示,但是由于该ICG的gating cell采用的是与门,此时cl

为低电平,即使enl有毛刺信号,也不能通过与门,因此该毛刺信号被过滤。

2)en信号出现在clk高电平期间,如下图所示

由于ICG中的latch是低电平有效,所以在clk高电平期间,latch采集不到en中的毛刺信号,因此该毛刺信号被过滤掉了。

综合以上,可以发现,无论en中的毛刺信号出现在clk低电平或者是高电平期间,ICG可以有效过滤掉en信号中的毛刺,得到好的clk波形!具体的ICG电路及其波形图如下所示

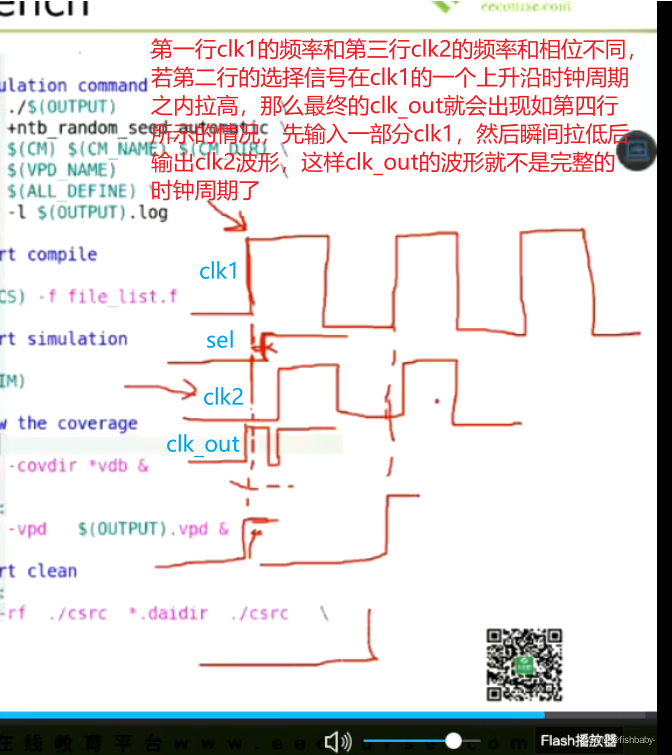

3、SoC系统中时钟切换应用场景