超前进位加法器(Verilog&数字IC)

在说到超前加法器之前,先要了解普通全加器。

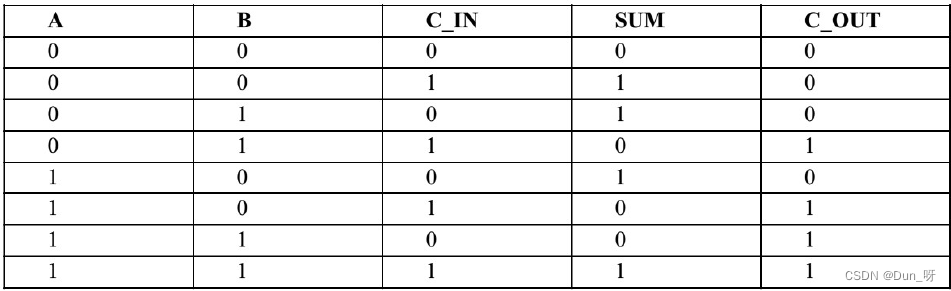

首先画出全加器真值表

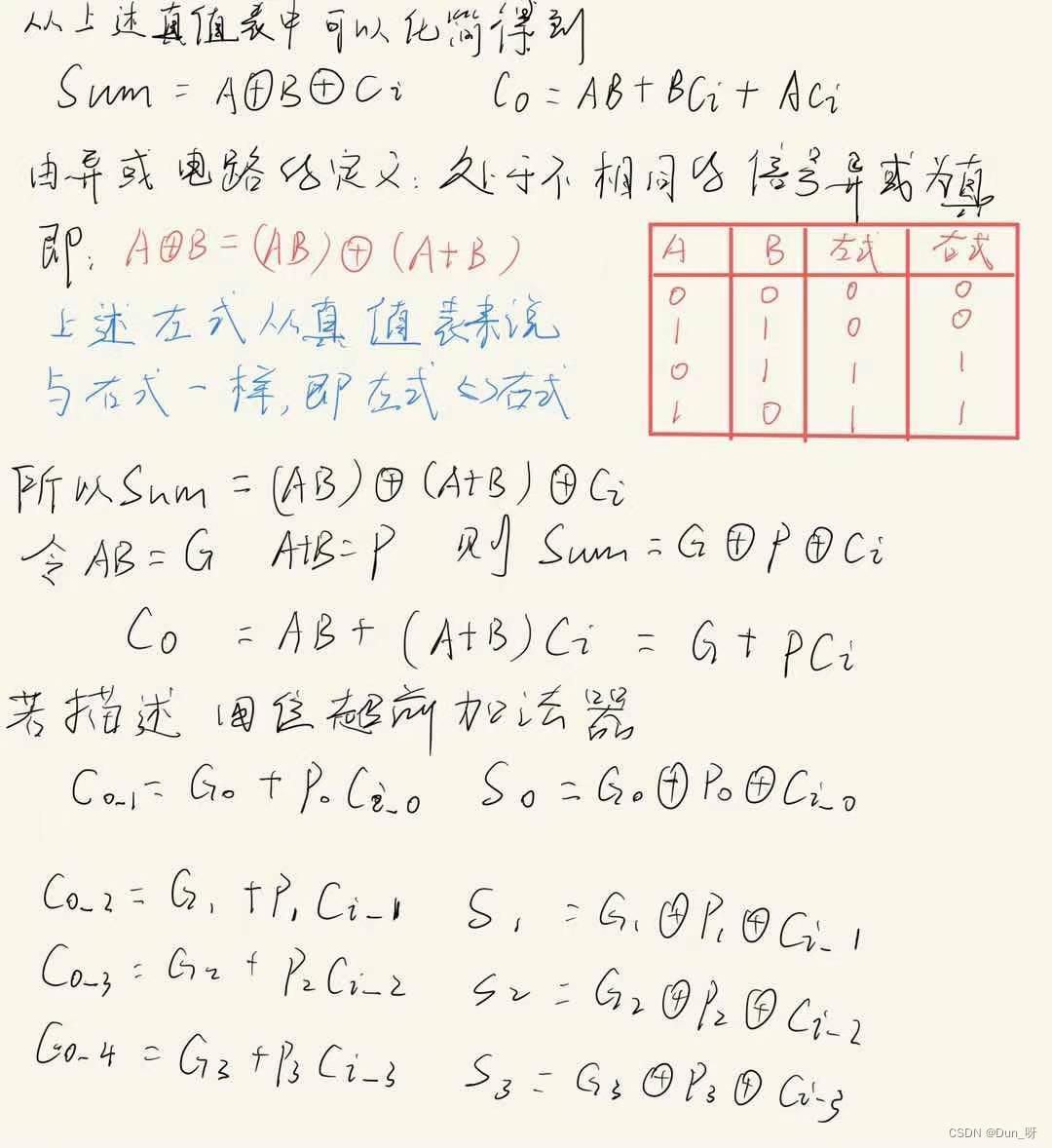

则此时可以写出Verilog代码:

module advance_adder(

input [3:0] a,

input [3:0] b,

input c_in,

output [3:0] sum_out,

output c_out

);

wire [4:0] g,p,c;

assign g=a&b;

assign p=a|b;

assign c0=c_in;

assign c1=g[0]|(p[0]&c[0]);

assign c2=g[1]|(p[1]&(g[0]|(p[0]&c[0])));

assign c3=g[2]|(p[2]&(g[1]|(p[1]&(g[0]|(p[0]&c[0])))));

assign c4=g[3]|(p[3]&(g[2]|(p[2]&(g[1]|(p[1]&(g[0]|(p[0]&c[0])))))));

assign sum_out = p^g^c[3:0];

assign c_out = c[4];

endmodule

普通加法器需要等进位完成才计算下一位,这样在计算大大增加了运算的时间,而超前进位加法器可以直接计算出所有全加器的进位输入信号,无需像普通加法器一样从最低位开始像最高位逐位传递信号。