PS部分实现helloworld

Hello World 是由 PS 部分的 UART 和 CPU 上的软件输出的。主要部分是 PS 端实现,第一步我们将在 Vivado 中制作硬件;之后,在SDK中编写Hello World软件。

在 Vivado 中创建硬件

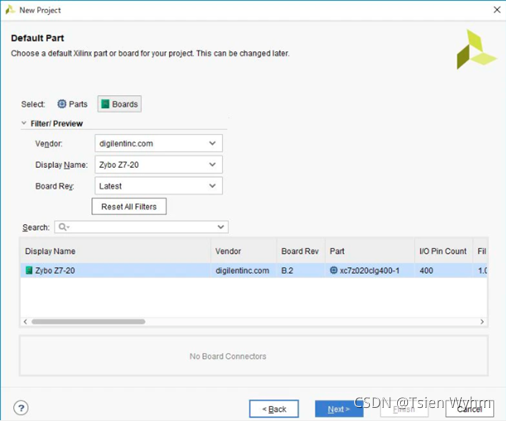

启动 Vivado。选择文件 - >新项目。设置项目的保存目的地和项目名称。这里,项目名称是“project_1”。项目类型应为“RTL 项目”。选择“板”。然后选择 digilentinc.com 作为您的供应商。选择 Zybo Z7-20 作为显示名称。

制作PS端硬件

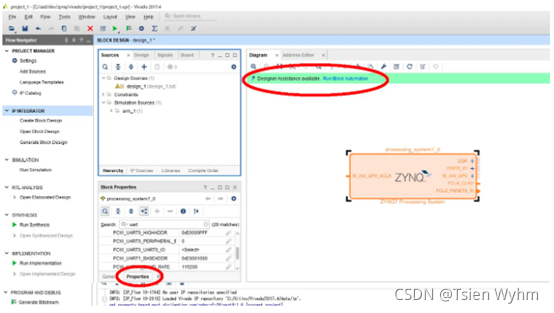

使用左侧的 Flow Navigator-> IP INTEGRATOR-> Create Block Design 创建一个新的块设计。将默认名称保留为 design_1。

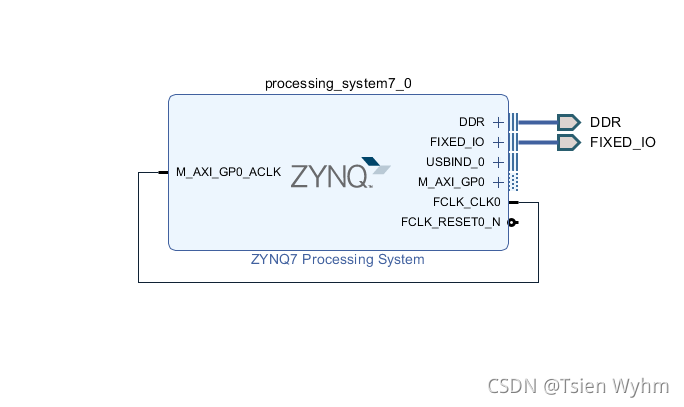

在图表视图中单击“按 + 按钮添加 IP”并选择“ZYNQ7 Processing System”。然后,将放置 PS 部分。然后单击屏幕上的“运行块自动化”。将出现设置窗口屏幕,确保选中“Apply Board Preset”并单击“确定”。

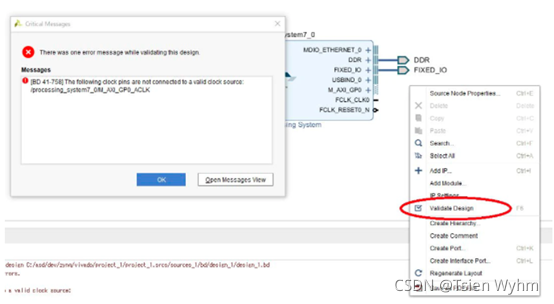

检查创建的块设计

可以通过右键单击图表视图并选择验证设计来检查它。即使是这么简单的设计,也发生了错误。原因是时钟没有正确提供给 M_AXI_GP0_ACLK。

修改块设计

AXI 是用于连接 IP 的总线。当 PS 成为主机并连接到其他从机 IP(例如 AXI GPIO)时使用。M_AXI_GP0_ACLK 是底层时钟。这次没有使用,可以通过关闭AXI_GP0本身的主控功能来纠正,这次我会通过正确设置时钟供应来解决。PS有一个名为FCLK_CLK0的端口,它看起来像一个 50MHz 的输出,将FCLK_CLK0 和 M_AXI_GP0_ACLK连接。

再次尝试验证设计,错误就会消失。

完成硬件设计

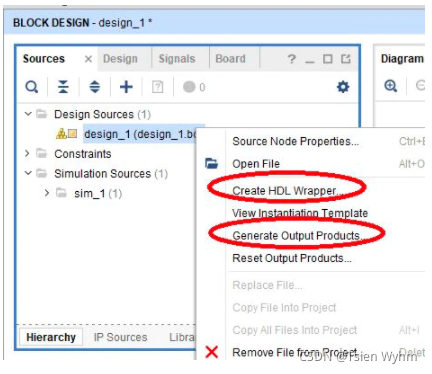

以上,仅PS部分的块设计就完成了。对于Hello World,只需要一个CPU和一个UART。将此块设计用作顶层设计。首先,生成一个输出文件并创建一个源文件。接下来,创建用于整个设计流程的 HDL 包装器。

具体来说,在“BLOCK DESIGN”->“Sources”选项卡上,右键单击此设计(“design_1”)。

1)生成输出产品-> 生成

2)创建 HDL Wrapper-> OK

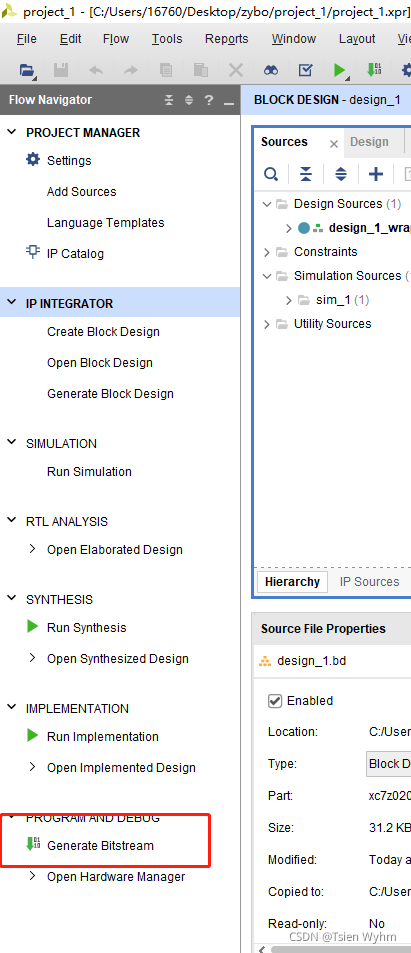

导出硬件位流文件

现在硬件已经完成,导出它。输出结果是一个称为比特流 (* .bit) 的文件。点击左侧的Flow Navigator-> PROGRAM AND DEBUG-> Generate Bitstream。结果,执行逻辑综合和布局布线并生成比特流文件。生成需要一些时间。完成后,将出现一个弹出窗口。结果保存在 project_1\project_1.runs\impl_1\design_1_wrapper.bit 中

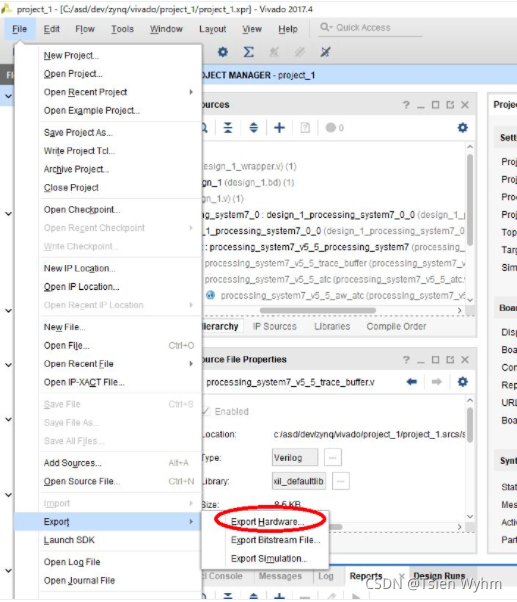

导出生成的比特流以方便软件(Xilinx SDK)使用。菜单栏-> 文件-> 导出-> 导出硬件。

启动Xilinx SDK

Vivado-> File-> Launch SDK-> OK 上的菜单栏,在 Vivado 中创建的硬件启动软件开发环境。具体来说,Xilinx SDK 将自动启动并创建 hw_platform 文件夹,之后生成C源代码,将比特流文件复制到hw_platform文件夹,并设置PS所需的时钟。hw_platform 文件夹是一个文件夹,汇总了目标硬件(之前创建的硬件)的信息。

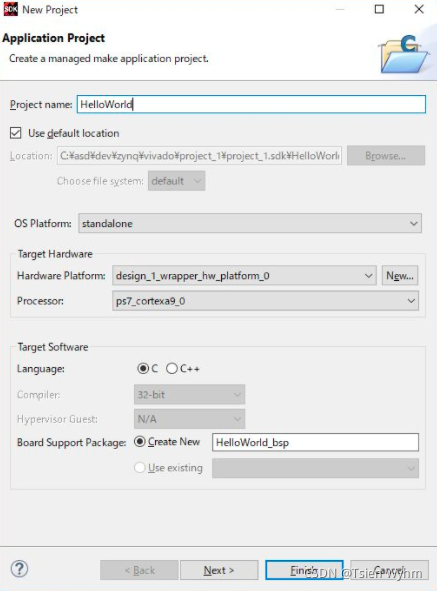

创建SDK项目

使用SDK上的菜单栏->新建->应用程序项目创建一个新的软件项目。从这里开始,它与正常的微机软件开发相同。使用以下设置创建一个项目。

项目名称:HelloWorld

操作系统:无

硬件:之前在 Vivado 中创建的硬件 (design_1_wrapper_hw_platform_0)

运行 CPU:CPU0

语言:C语言

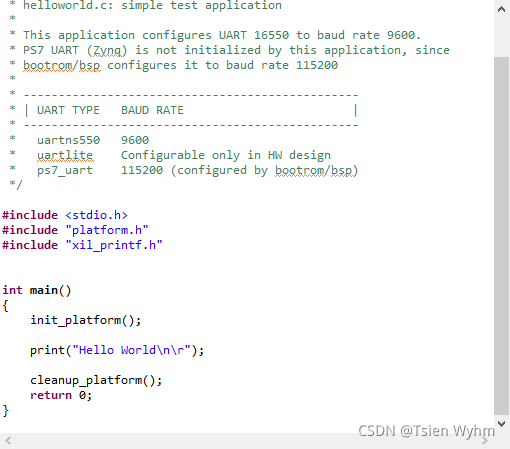

编写源代码

编写代码以从 UART 输出 Hello World,这里使用自动生成的代码。

开发板跳线检查

改变ZYBO板上JP5的跳线连接,短接JTAG区域(默认为QSPI),可以通过 JTAG (USB) 写入这次创建的硬件。将 USB 电缆插入板上的微型 USB 端子 连接到 PC,打开电源。

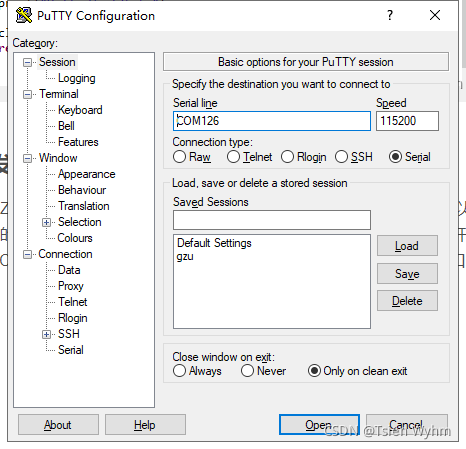

在 PC 端,启动相应的终端软件(例如 Putty)并连接到 USB 串行端口。波特率应为 115200。

导入比特流文件

写入硬件信息(比特流文件),在菜单栏-> Xilinx-> Program FPGA 中,会显示如下窗口。这为 ZYBO 提供了刚刚在 Vivado 中创建的硬件配置。关闭/打开电源或重置后,需要再次写入。

运行程序

在 Project Explorer 上选择 Hello World 项目。

运行:菜单栏-> 运行方式-> 在硬件上启动(系统调试器),或播放按钮

调试:菜单栏-> 调试为-> 在硬件上启动(系统调试器),或错误按钮

运行时,在终端Hello World显示成功。

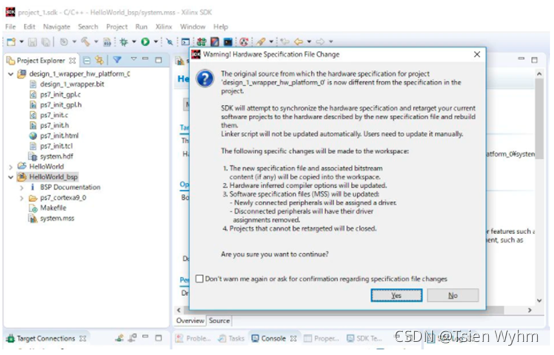

更新硬件设计

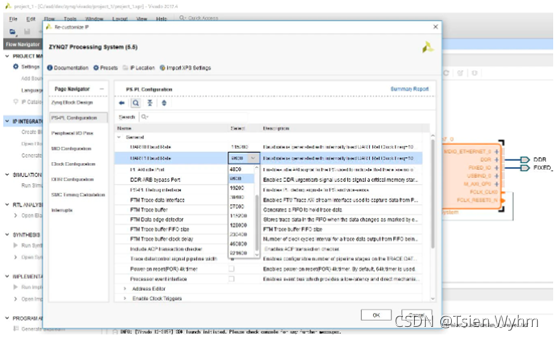

假设已经在 Xilinx SDK 上创建了一个项目,并在开发软件时更改了硬件端(hdf 文件)。这些更改也需要反映在 SDK 中。作为测试,尝试将 UART 波特率从 115200 更改为 9600。

返回 Vivado 并打开 design_1 的模块设计,在图表视图中双击 PS 以打开属性屏幕。尝试将 UART1 的波特率更改为 9600,如下所示。

然后再次重新生成输出产品,创建 HDL 包装器、生成比特流、导出硬件(包括比特流)。

最后,SDK端的屏幕上会显示如下窗口,并且会自动更新。