VCS-Verdi仿真

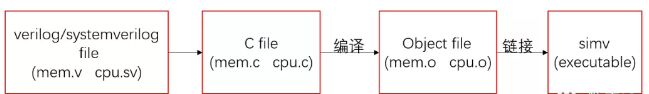

VCS和Verdi仿真:

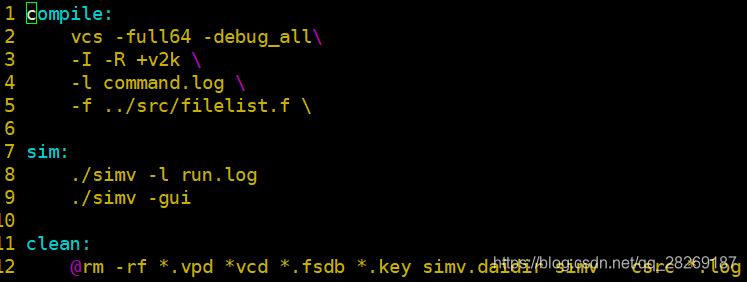

makefile用法:

make_vcs、verdi、clean(编译、仿真、查看波形、清除)

-Mupdate 增量编译,只重新编译变化的文件。

-R 编译完后自动仿真。-l 设置log文件。 +v2k 支持verilog2001.

-f 将RTL路径整合到filelist.f文件中。 -o foo,改变simv名字为foo。

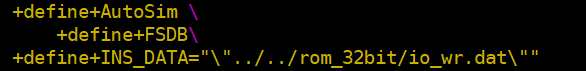

+define+<宏名称>=<值>。

+incdir+inc路径 在当前路径下找文件

波形分析:

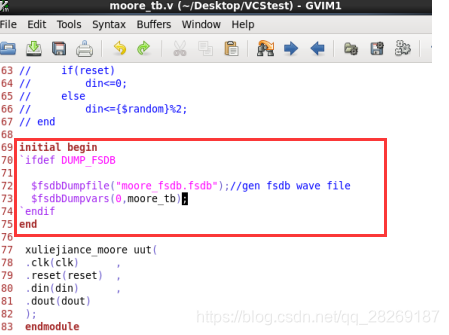

1:vcs和verdi联合仿真条件

①生成的“.fsdb”文件才能用于Verdi波形分析。

②要生成“.fsdb”文件,需要在Testbench中加入图2所示的几行用于产生“.fsdb”文件代码。

③注意环境变量的添加:.bashrc文件

2:vcs和verdi仿真快捷键

①抓取波形nwave,点击波形窗口后(大写字母=shift+小写):

快速抓信号:选取后ctrl+w。添加波形:g(get signal)。

放大、缩小波形:小写z缩小(zoom ),shift+z放大。波形全部显示:f(full)。

翻转信号跳转:n(next)向前,N向后。

改变信号颜色:c(color)。

重新加载设计:file->reload design。

②

debug经验:

①使用系统函数:

$time、display、monitor、stop、finish、readmemb、readmemh

②$fsdbDumpMDA();用verdi查看二维数组信号。

③覆盖率:代码覆盖率和功能覆盖率

代码覆盖率:检查if和else if完整、各路径是否都跳转、检查语句是否被执行、检查状态机每个状态是否达到。