多时钟--RTL前仿真,仿真工具误采样问题

在数字设计中,会遇到处理多个时钟的问题(如下面的a_clk、apb_clk),虽然在综合时,会将处于同一个时钟域的clock放在一个group中,保证了时序的同步性。但是,在RTL前仿中,仿真工具不会对其进行识别,会认为多个时钟处于不同的时钟域,从而会出现采样位置不对的现象。

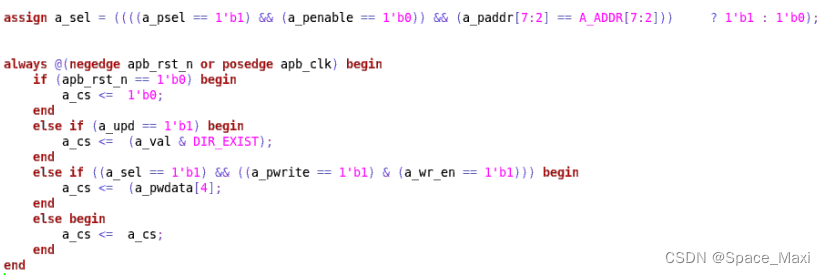

下面的逻辑,组合逻辑信号a_sel处于a_clk下,a_cs时序逻辑处于apb_clk下。

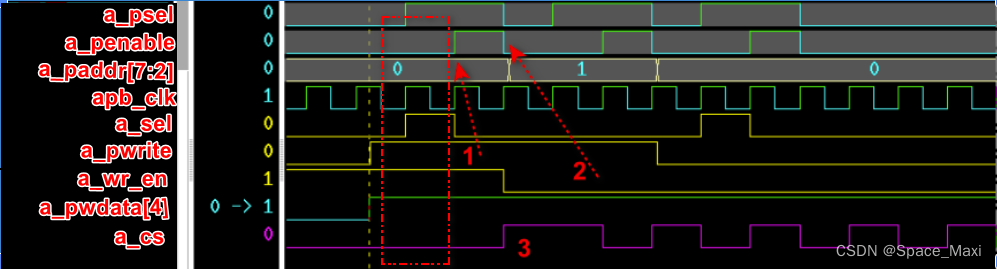

简单的仿真结果如下:

从上面RTL仿真可以看出:

位置1处:

虽然a_sel拉高了,apb_clk按道理应该采样到该信号,然后a_cs拉高,但是结果并非如此。这是因为仿真工具对不同的时钟域之间的信号分析后,判定为此处采样不到高电平。

位置2处:

虽然a_sel拉低了,apb_clk按道理应该采样不到高电平信号,但是结果并非如此。这是因为仿真工具,对不同的时钟域之间的信号分析后,判定为此处可以采样到高电平,所以位置3处a_cs拉高。

在设计仿真阶段,一定要注意该问题,不然会造成仿真结果与实际设计出现误差,或者RTL仿真与后仿真结果不一致,浪费时间去排查问题。

在RTL设计阶段,可以采用# delay将信号的相位错开,来保证前仿真阶段的逻辑正确性,避免时钟域的误判段问题。