软考-计算机系统

软考-计算机系统

CPU运算器

算术逻辑单元(ALU)负责算术运算和逻辑运算

累加寄存器(AC) 运算操作数和结果的寄存器

数据缓存寄存器(DR)CPU和其他设备之间的中转站

状态条件寄存器(PSW)略

CPU控制器

指令寄存器(IR)存放的是从内存中取得指令,就像个中间站一样,不过是存放指令的中间站

程序计数器(PC)存放的是指令的地址,还有计数的功能

地址寄存器(AR)存放的是cpu访问内存单元的地址

指令译码器(ID)是把操作码解析成对应的指令操作

原码

正数:符号位取 0

- [+1]原 = 0 000 0001

负数:符号位取 1

- [-1]原 = 1 000 0001

反码 负数:符号位不变,数值位置取反

- [-1]反 = 1 111 1110

补码 负数:符号位不变,数值位置取反,最后加1

即反码加一

- [-1]补 = 1 111 1111

移码

移码最简单了,不管正负数,只要将其补码的符号位取反即可。

正数:正反补一致

- [+1]补 = 0 000 0001

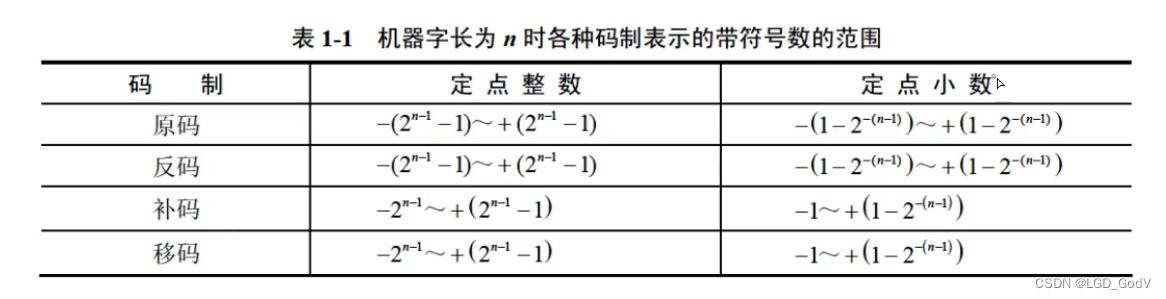

机器码范围

0的机器码

- [+0]原码=0 000 0000, [-0]原码=1 000 0000

- [+0]反码=0 000 0000, [-0]反码=1 111 1111

- [+0]补码=0 000 0000, [-0]补码=0 000 0000

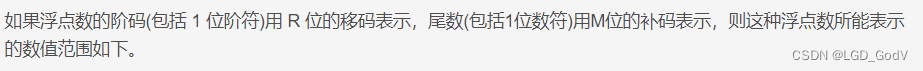

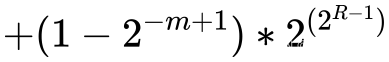

浮点数运算

- 浮点数表示取值范围由阶码决定(e)精度由尾数决定

- 小数点不需要占位

最大范围

最小范围

1.海明码

可纠错可检错,公式:

2.奇偶校验码

只能检错,不纠错。只能检测奇数个数位出错,偶数个数位不可以。码距2。

- 可以检错,但不能纠错,码距2。

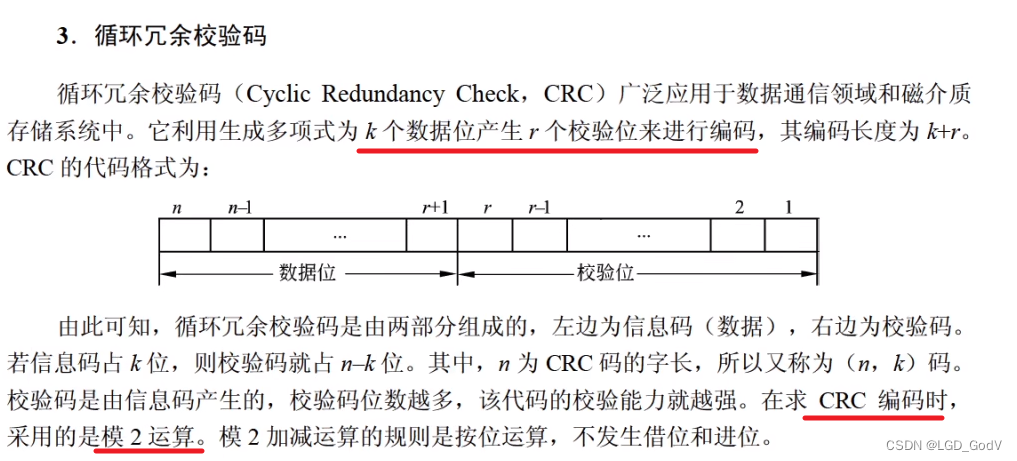

- 编码长度:k个数据位+r个校验位

- CRC编码采用模2运算

RISC / CISC

流水线

流水线的总共时间 = 一条完整指令的时间 +(n-1)* 最长时间段

吞吐率=指令条数 / 流水线总共时间

存储器

存储系统的层次结构(由上到下)

- CPU内部通用寄存器 访问速度最快

- Cache高速缓冲 主要用SRAM静态随机存储器 (我的理解是 在于内存和CPU之间的一层存储单元)

主存储器 (我的理解是 硬盘) - (SRAM静态随机存储器、DRAM动态随机存储器–需要周期性的刷新,主存主要由这个构成)

存储器的工作方式

-

读 / 写存储器 RAM

-

只读存储器

-

固定只读存储器ROM

-

可编程只读存储器PROM

-

可擦除可编程的只读存储器 EPROM

-

电擦除可编程的只读存储器 EEPROM

-

闪速存储器,闪存(优盘)。块为单位删除,信息不会丢失 ,代替ROM不可以代替主存

访问方式分类:地址访问和内容访问

相联存储器 是按 内容访问的存储器

寻址方式分类

- 随机存储器RAM

- 顺序存储器SAM

- 直接存储器DAM

虚拟存储器

由主存和辅存构成的,里面的CPU有空间(会访问旁边空间的地址)、时间(过段时间会再次访问)局部性

Cache高速缓存

重点:cache与主存地址的映射是由硬件自动完成、对于程序员是透明

Cache地址映像冲突(从小到大排序)

- 全相联映像 (小)

- 组相联映像 (中)

- 直接映像 (大)

中断

- 中断向量(断点)提高中断服务程序的入口地址

- 中断响应时间:发出中断请求开始到中断服务程序

输入输出(I/O)控制方式

- 程序查询方式

IO与CPU串行 - 中断驱动方式

IO与CPU并行 - 直接存储器存储方式(DMA)

IO与CPU串行

开始与结束时才有CPU干涉

一次读写的单位为“块”而不是字

由外设直接将数据存入内存

加密

对称密钥

- DES

- 3DES

- RC-5

- IDEA

- AES

- RC4

非对称密钥

- RSA

- ECC

- DSA

其余

Hash 函数

MD5 摘要算法

SHA-1 安全散列算法

可靠性公式

串联系统

R=R1 * R2 * R3 *…Rn

并联系统

R=1-(1-R1)*(1-R2)…(1-Rn)