Simulink-过零检测与代数环

过零检测

过零检测即通过Simulink为模块注册若干过零函数,当模块变化趋势剧烈时,过零函数将会发生符号变化。每个采样点仿真结束时,Simulink检测过零函数是否有符号变化,如果检测到过零点,则Simulink将在前一个采样点和目前采样点之间内插值。

以下列出了Simulink 中支持过零检测的模块。

Abs 一个过零检测:检测输入信号沿上升或下降方向通过零点

Backlash 两个过零检测:一个检测是否超过上限阈值,另一个检测是否超过下限阈值

Dead Zone 两个过零检测:一个检测何时进入死区,另一个检测何时离开死区

Hit Crossing —个过零检测:检测输人何时通过阈值

Integrator 若提供了Reset端口,则检测何时发生Reset;若输出有限,则有3个过零检测,即检测

何时达到上限饱和值、检测何时达到下限饱和值和检测何时离开饱和区

MinMax 对于输出向量的每个分量,当输入信号是新的最小值或新的最大值时,进行检测

Relay 一个过零检测:若Relay是 off状态,则检测开启点:若是on状态,则检测关闭点

Relational Operator 一个过零检测:检测输出何时发生改变

Saturation 两个过零检测:一个检测何时达到或离开上限,另一个检测何时达到或离开下限

Sign 一个过零检测:检测输人何时通过零点

Step 一个过零检测:检测阶跃发生时间

Switch 一个过零检测:检测开关条件是否满足

Subsystem 用于有条件地运行子系统:一个使能端口,一个触发端口

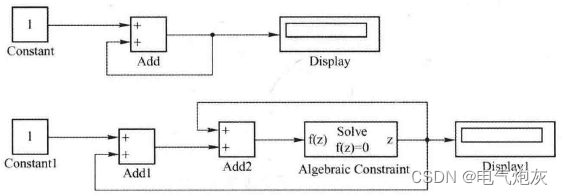

代数环

如果Simulink 的输入依赖于模型中某一模块的输出,就会产生一个代数环,如图所示。这意味着无法进行仿真,因为没有输入就得不到输出,没有输出也得不到输入,形成了一个死循环。

解决代数环的办法有以下4种。

1、采用替代结构,尽量不形成代数环的结构。

2、为可以设置初始值的模块设置初值。

3、对于连续系统,在模块的输出一侧增加memory模块。

4、对于离散系统,在模块的输出一侧增加 unit delay模块。