VCS的使用笔记

VCS

VCS是一个编译型Verilog仿真器,用于验证数字电路设计的正确性。VCS可以进行逻辑仿真、时序仿真和功耗仿真。

VCS的工作流程如下:

- 将Verilog或SystemVerilog代码转化为C代码。

- 在Linux环境下使用C编译器编译C代码,并链接库文件,生成可执行文件。

- 运行生成的可执行文件,对设计进行仿真。

vcs source_files [compile_time_options]命令:用于编译Verilog代码,并生成可执行文件(simv)用于仿真。

其中,source_files 指定了要编译的源文件列表,可以是多个文件,文件名之间用空格分隔。 compile_time_options 是编译时的选项,指定VCS如何进行编译,例如优化级别、调试信息等。

常见的[compile_time_options]

-Mupdate:增量编译。当需要对一个或多个文件进行修改并重新编译时,使用-Mupdate命令可以避免重复编译,从而节省时间。

-R:编译后立即执行。

-gui:图形化界面

-l <filename>:保存一些运行时的log文件

-sverilog:支持SystemVerilog

-v lib_file:表示将库文件lib_file加入vcs的库搜索路径中。如果RTL代码中有IP,vcs会在lib_file这个文件中去搜索这个IP

-y lib_dir: 添加一个路径,用于搜索模块定义

+libext+:在lib库中搜索指定后缀名的文件

+incdir+<directory>:将 <directory> 添加到头文件搜索路径中,以便编译器可以找到在源代码中使用 ``include 包含的文件。 假设有一个名为 'example.v'的 Verilog 源代码文件包含:include “header.h”,而header.h在/home/user/include目录下,则可以使用命令:vcs +incdir+/home/user/include example.v`

-f file:指定一个文件作为VCS命令行参数的输入源。每个参数占据文件中的一行。

-o filename:改变生成的可执行的文件的名字,不叫simv了

仿真过程

simv [run_time_options]:[run_time_options]制定了vcs如何执行仿真

常见的[run_time_options]

-s:停止仿真

-l logfile:把仿真时的输出和日志存到logfile文件中

在VCS中使用DesignWare库

DesignWare 库是 Synopsys 公司提供的一个硬件 IP 核库,包含了许多用于 SoC 设计的可重用 IP 核和子系统。

vcs -v $DW_ROOT/dw/sim_ver/:把DW库的路径添加到搜索路径中,其中DW_ROOT就是DW库的根目录。

当然verilog代码中也要include的所用的模块,比如:``include “dw/axi_master/verif/dw_axi_master.sv”`

VCS debugging

命令行debug:UCLI,不好用、不常用

verdi:专门用于debug

DVE:vcs的GUI界面

要考虑的方面:仿真速度、信号可见性、信号可追踪性tractability、可用性

出现bug时,要能够追踪到故障的来源;同时监测多个信号要保证其准确性

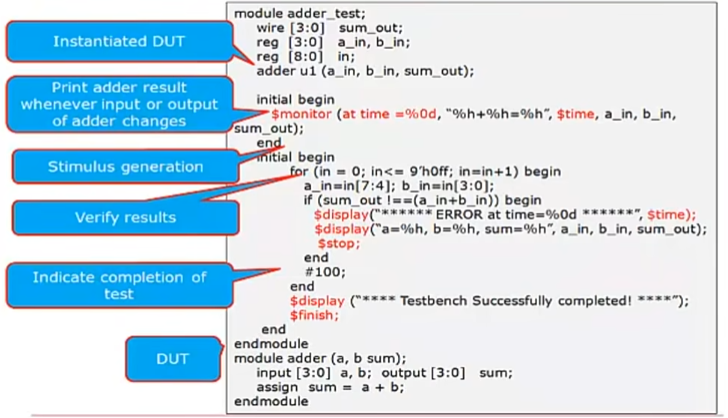

用于debug的Verilog系统任务

$display: 把信息显示到终端上

$monitor:监控信号列表。在一个周期内比display稍微晚一点,是在赋值结束之后才调用。

$time:返回当前的仿真时间

$stop:中止仿真(暴力kill)

$finish:终止仿真(让仿真正常结束,做一些收尾工作),一般采用$finish

$readmemh:读取内存初始化文件(十六进制)

$readmemb:同上、二进制

CTRL-C退出死循环;或者直接kill进程

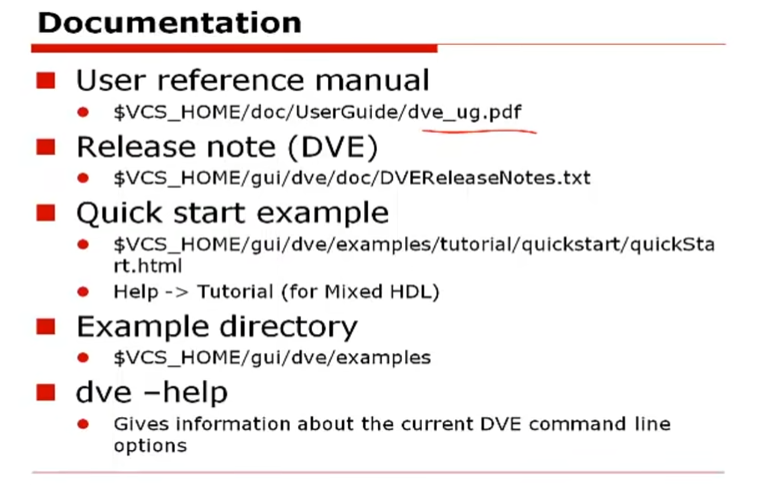

用DVE进行debug

DVE的启动:

vcs xxx.v -R -gui -debugall: 编译后立即启动DVE进行仿真和debug

simv -gui:已经生成了可执行文件后也可以这样启动

如果使用post-process mode,也可以先用dve直接启动,然后再open database(.vcd, .vpd文件)

(Verdi支持fsdb)